Цифровые устройства

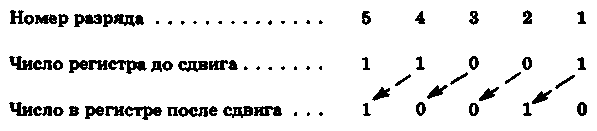

Регистры. Функциональное устройство, принимающее и запоминающее кодовое слово, а также выполняющее над словом некоторые логические операции, называют регистром. Под кодовым словом понимают последовательность двоичных цифр определенной длины. Регистр представляет собой совокупность триггеров, число которых соответствует числу разрядов в слове. Так, например, кодовое слово 01100 имеет пять разрядов и для его хранения необходим регистр из пяти триггеров. Прием информации в триггеры регистра (рис. 1.25, а) осуществляется подачей на входы х, Х2, хз сигналов, соответствующих логическим переменным при поступлении синхросигнала С. Предварительно перед занесением в регистр кода числа необходимо его «очистить» с помощью операции Установка в нуль. Информация, записанная в регистр, хранится до следующей установки регистра в нуль. В устройствах связи и вычислительной техники часто используют сдвигающие регистры. Ниже показан пример сдвига числа на один разряд влево при использовании пятиразрядного регистра.

Суть сдвига состоит в том, что цифра, имевшаяся в г-м разряде регистра до сдвига, передается в соседний слева (г»+1)-й разряд, а цифра (г»+1)-го разряда — в (/+ 2)-й разряд и т. д. Крайний правый разряд заполняется нулем, а цифра крайнего левого разряда, выдвигаясь из регистра, теряется.

Выход триггера предыдущего разряда (рис. 1.25,6) подключен к входу Э триггера последующего разряда, поэтому с приходом каждого синхроимпульса С состояние триггера /-го разряда повторяет состояние триггера (г-1)-го разряда в предыдущем такте.

Рис 1 25 Функциональная схема трехразрядного регистра памяти на триггерах (а) и «-разрядного регистра сдвига на О триггерах (б)

Информация в параллельном коде записывается по входам 5 триггеров, а в последовательном коде — по входу И триггера фи

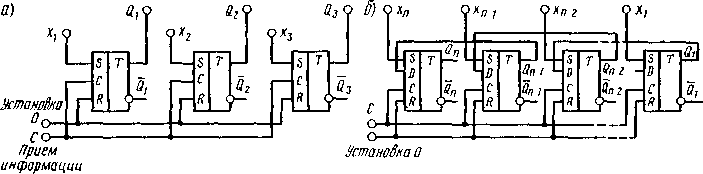

Счетчики импульсов и делители частоты. Устройство, подсчитывающее число импульсов, поступающих на его вход, и фиксирующее это число в виде кода, хранящегося в триггерах, называют счетчиком. В счетчиках имеется один вход, на который поступают счетные импульсы х

сч

, и п выходов, соответствующие числу триггеров. Максимальное число, до которого может вестись счет Ы-2

п

-1. Так, при п= 5 N-31. Схема трехразрядного (п= 3) счетчика выполнена на //(-триггерах (рис. 1.26). Допустим, что в начальный момент времени 1= 0 все триггеры находятся в состоянии 0. На входы / и К всех триггеров поданы постоянно сигналы, соответствующие коду 1, поэтому каждый из триггеров изменяет состояние под воздействием каждого импульса, поступающего на его вход С. Таким образом, триггер С?, будет перебрасываться от каждого импульса, поступающего на счетный вход х

сч

, триггер фз меняет состояние при каждом импульсе, поступившем с выхода фи т. е. в 2 раза реже, чем фи а триггер фз перебрасывается при каждом импульсе, поступившем с выхода фг, т. е. в 2 раза реже, чем ф

2

. Временная диаграмма построена исходя из того, что триггеры переключаются по заднему фронту импульсов на их входах. После восьми импульсов, поступивших на вход х

сч

, триггеры переходят в исходное нулевое состояние. Как следует из таолицы состояний триггеров счетчика (табл. 1.5), каждому числу приходящих на вход х

сч

импульсов соответствует определенная комбинация состояний триггеров Ф1Ф2Ф3.

Делитель частоты — устройство, которое при подаче на его вход периодической импульсной последовательности формирует на выходе

Рис 1 27 Структурная схема дешифратора на два входа (а) и его условное обозначение (б)

такую же последовательность, но имеющую частоту повторения импульсов, в определенное число раз меньшую, чем частота повторения импульсов входной последовательности.

Схема (см. рис. 1.26, а) решает задачу деления частоты на Ы- 8 при использовании в качестве выхода делителя частоты — выхода триггера фз- Из временной диаграммы (см. рис. 1.26,6) следует, что период переключения триггера С?з в 8 раз больше периода импульсов, поступающих на вход схемы делителя х

сч

.

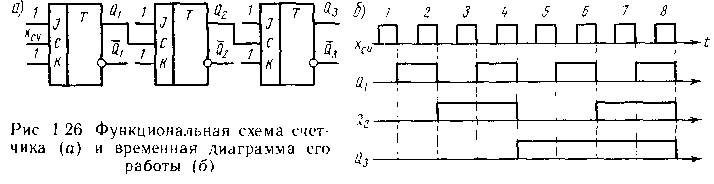

Дешифраторы и шифраторы. Цифровой автомат, имеющий п входов, т выходов и преобразующий комбинацию двоичных сигналов (код числа) в выходной единичный сигнал только на одном из его выходов, называют дешифратором (декодером). Соотношение между тип определяется выражением т= 2″. При двух входах х и х

2

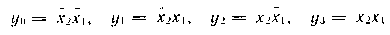

(рис. 1.27) дешифратор имеет четыре выхода уо, уь ?/2, Уз- Значения четырех выходных переменных определяются логическими выражениями:

Для функционирования этого дешифратора необходимо присутствие на входах прямых х хч и инверсных х

х

х% значений переменных. Обычно входные сигналы дешифратора поступают от триггеров регистра или счетчика, имеющих прямые и инверсные выходы. Аналогичным образом с использованием элементов И могут быть построены дешифраторы и на большее число входов.

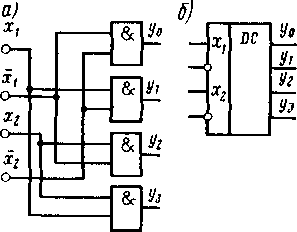

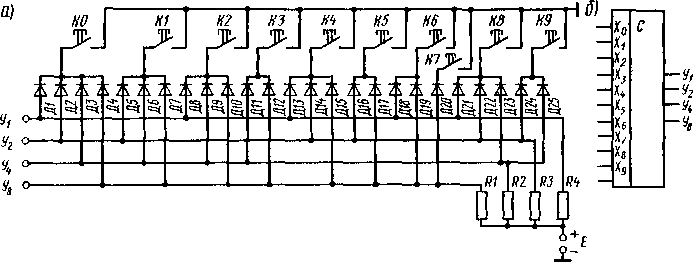

Шифратором (кодером) называют комбинационное логическое устройство, преобразующее сигналы сообщений (буквы, цифры, символы), поступающие на один из входов, в совокупность сигналов (кодовую комбинацию). На схеме (рис. 1.28) изображены ряд кон-

Таблица 15

|

Число импульсов, поступивших на вход |

Состояние триггера |

||

|

<3. |

<Э> |

<3. |

|

|

Исходное состояние |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

2 |

0 |

1 |

0 |

|

3 |

1 |

1 |

0 |

|

4 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

|

7 |

I |

1 |

I |

|

8 |

0 |

0 |

0 |

Таблица 16

|

Нажатая кнопка |

Выходы |

|||

|

У і |

Ч> |

У4 |

Уь |

|

|

ко |

0 |

0 |

0 |

0 |

|

К1 |

1 |

0 |

0 |

0 |

|

К2 |

0 |

1 |

0 |

0 |

|

КЗ |

1 |

1 |

0 |

0 |

|

К4 |

0 |

0 |

1 |

0 |

|

К5 |

1 |

0 |

1 |

0 |

|

Кб |

0 |

1 |

1 |

0 |

|

К7 |

1 |

1 |

1 |

0 |

|

К8 |

0 |

0 |

0 |

1 |

|

К9 |

1 |

0 |

0 |

1 |

Рис 1 28 Функциональная схема шифратора на десять входов (а) и его условное

обозначение (б)

тактов, соответствующих клавишам от КО до К9, и четыре выходные шины і/8, У4, У2, У і- Данный шифратор преобразовывает десятичные числа от 0 до 9 в четырехразрядный двоичный код в соответствии с табл. 1.6.

При нажатии, например, кнопки Кб диоды Д18 и Д19 открываются и на горизонтальных шинах у и у% потенциал снижается, на шинах же ?/г и г/

4

потенциал остается высоким, т. е. десятичное число преобразуется в четырехзначное двоичное число

(/8=0, 1/4=1, (/2=1, (/1=0

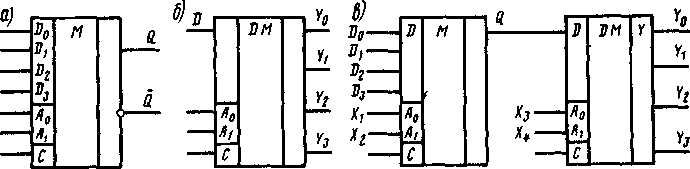

Мультиплексоры и демультиплексоры. Мультиплексор имеет п

к

информационных ВХОДОВ Оо /Лги- I и п

а

адресных ВХОДОВ Ао, А і, …. Апа-1, вход для подачи импульса синхронизации С и один выход ф. Соотношение между числом информационных и адресных входов определяется выражением п„= 2″“. На рис. 1.29, а показано символическое изображение мультиплексора с двумя адресными входами Ао и А. Каждому информационному входу мультиплексора присваивают номер, называемый адресом. При подаче сигнала синхронизации С= 1 мультиплексор выбирает один из входов, адрес которого задается двоичным кодом на адресных входах, и подключает его к выходу. Функционирование мультиплексора определяется табл. 1.7.

Рис 1 29 Условное обозначение мультиплексора (а), демультиплексора (б) и схема объединения мультигутексора с демультиплексором (в)

Из таблицы следует, что если сигнал синхронизации С= 0, то в независимости от сигналов на адресных входах 0. При С= 1 на выход передается логический сигнал того из информационных входов А, номер которого в двоичной форме задан на адресных входах.

Демультиплексор — устройство, имеющее один информационный вход А п

а

адресных входов Ло, А, …, А

Па

— 1 и т выходов у

0

у, …, у

т

-, а также вход синхронизации С.

Соотношение между числом адресных входов п

а

и числом выходов т определяется соотношением т=2

Па

. На рис. 1.29,6 показано условное обозначение демультиплексора с двумя адресными входами, а его функционирование определяется табл. 1.8.

Из таблицы следует, что сигнал с входа О передается на выход ?/,, номер которого в двоичной форме задан на адресных входах. Если на вход ?> демультиплексора подавать константу /)= 1, то на выбранном в соответствии с заданным адресом выходе будет логическая 1, а на остальных -«логический 0, т. е. демультиплексор выполняет функцию дешифратора.

Объединяя мультиплексор с демультиплексором (рис. 1.29, в), можно реализовать устройство, в котором по заданным адресам один из входов А; А; А; А подключается к одному из выходов у

0

; г/1; г/

2

; Уз- Данное устройство обеспечивает любую комбинацию соединений входов с выходами. Так, например, при комбинации адресных входов х= 0; х

2

= 1; х

3

= 1; х- 1 и с= 1 вход Д1 окажется подключенным к выходу Уз, т. е. Уз- А.

Сумматоры. Узел, выполняющий операцию суммирования двух чисел, называют сумматором. Сумматор для сложения многоразрядных чисел представляет соединение одноразрядных сумматоров, каждый из которых имеет три входа для подачи цифр, разрядов слагаемых а,, Ь,, переноса р, из предыдущего разряда г- 1 и два выхода — суммы 5, и переноса р,+1 для передачи в следующий разряд (рис. 1.30). Функционирование сумматора определяется табл. 1.9.

Используют два основных типа сумматоров: комбинационные и накапливающие. В комбинационных сумматорах результат на выходных шинах существует только во время выполнения

і а б л и ц а 17

а б л н ц а 18

|

Адресные входы |

Сигнал синхронизации, С |

Выход <2 |

Адресные входы |

Вход син хронизации |

Выходы |

|||||

|

Ай |

л, |

Ао |

Лі |

С |

У» |

У |

У і |

Уі |

||

|

X |

X |

0 |

0 |

X |

X |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

і |

?>о |

0 |

0 |

1 |

о |

0 |

0 |

0 |

|

0 |

і |

і |

Ох |

0 |

і |

1 |

0 |

о |

0 |

0 |

|

1 |

0 |

і |

0 |

і |

0 |

1 |

0 |

0 |

о |

0 |

|

1 |

1 |

і |

?>з |

1 |

і |

1 |

0 |

0 |

0 |

о |

|

Входы |

Выходы |

Входы |

Выходы |

|||||||

|

Слагаемые |

Перенос |

Сумма |

Перенос |

Слагаемые |

Перенос |

Сумма |

Перенос |

|||

|

а, |

Ь |

Р |

5, |

р +1 |

а |

Ь |

Р |

5 |

р.+> |

|

|

0 |

0 |

0 |

0 |

0 |

і |

0 |

0 |

і |

0 |

|

|

0 |

0 |

1 |

і |

0 |

і |

0 |

1 |

0 |

1 |

|

|

-о |

1 |

0 |

і |

0 |

і |

і |

0 |

0 |

1 |

|

|

0 |

1 |

1 |

0 |

1 |

і |

і |

1 |

1 |

1 |

|

операции. В накапливающих сумматорах результат определяет собой сумму действующего на входе слагаемого и внутреннего содержимого сумматора, предварительно в него занесенного. Накапливающие сумматоры, построенные с использованием запоминающих элементов, позволяют сохранить сумму и после выполнения операции.

⇐

Логические операции и элементы

|

Автоматика, телемеханика и связь на железнодорожном транспорте

|

Колебательные контуры и фильтры

⇒